Objectives

Implement a simple car alarm on a Xilinx Spartan 3 Starter kit board from Digilent, using the VHDL code exported from Multisim 12.0 in our first part of this tutorial,

In this second part we will implement and test the logic circuit of the Car Alam on a Xilinx FPGA Spartan 3 Starter kit board.

Workflow

A complete workflow of an FPGA design is normally:

- Problem/requirements analysis, vendor selection

- Behavioral model design

- RTL (Verilog or VHDL) design

- RTL verification

- Logic synthesis

- Implementation

- Static timing analysis

- Bitstream generation

The first two steps have already been taken in part I. In this part the next steps will be taken (except for Static timing analysis, obviously).

Requirements

– VHDL code from part I

– Digilent Spartan 3 Starter Kit board

– Xilinx ISE Design Suite 13.4 or superior

Implentation on FPGA

Launch Xilinx ISE Design Suite, get into the Project Navigator, and start a New Project pressing the button for New Project. Xilinx ISE Project Navigator controls all aspects of the development flow of our FPGA. We will use it to launch all development tasks.

Give the project a name such as Car_alarm and fill all the fields appropriately, including pointing to the drive and directory in your PC where you will keep the project files:

Press Next > button, and choose the fields again as shown:

Press again Next > and you will see the final window:

Press Finish and we will get back to the Xilinx ISE Project Navigator.

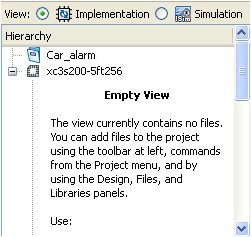

We will concentrate for now on Implementation and Hierarchy window:

We will add Car_alarm.vhd source (from part I of this post) , by pressing with the right button of the mouse on XC3S200-5FT256 and Add Source:

Car_alarm.vhd will now be part of our project Hierachy window:

If ones presses onto the Car_Alarm behavioral in Hierarchy window, the desktop window will show the code.

We will check the syntax in the Processes window just below the Hierachy window on the left side of workspace, by pressing with the right button of the mouse on Check Syntax:

Hopefull the syntax will be right and the Processes window will be now as shown below:

And the Console windows will report success:

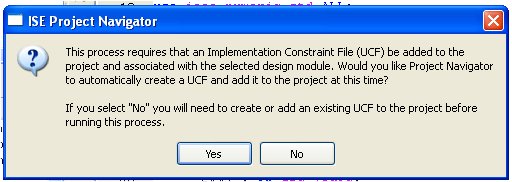

We will now add Constraints file in order to Synthetize next and implement the VHDL code. The Constraints file (UCF) will tell the Xilinx ISE the pins arrangements (I/O planning) of our Spartan 3 board.

The Contraints file can also have timing, offset, false and or multicycle paths, and other relevant constraints. In our case, with simple logic circuit, only I/O pin arrangements are required.

Our Xilinx ISE Project Navigator gives us an interface PlanAhead tool that permits the constraints file to be written. In Processess window press with the right button of the mouse I/O Planning (PlanAhead) and Run:

The following window will pop up:

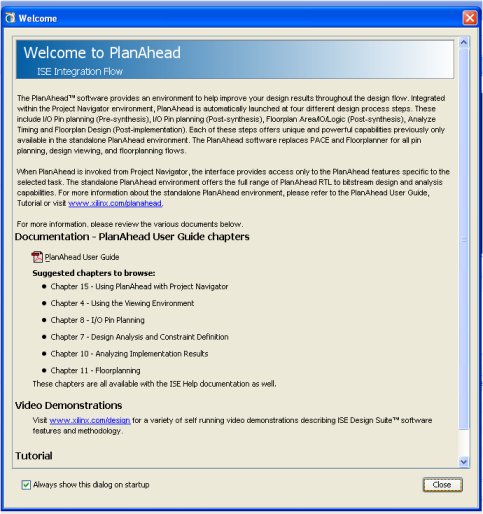

Press Yes button and PlanAhead will open. Once the start up has been made with our VHDL file, the following Welcome window will open:

The window show the link of PlanAhead User Guide pdf which is worth reading. Press Close button.

In PlanAhead within I/O Ports window expand the Scalar ports where you will see the 4 ports we defined in part I.

We will check the Digilent Spartan 3 User Manual to configure Contraints of the pins. In page 19 we see the slider switch connections:

In page 20 we see the LED connections:

DOOR will be SW2 i.e. H14;

KEY will be SW1 i.e. G12;

SEAT will be F12;

and ALARM will be LD0 i.e. K12.

Hence within Site of I/O ports we will introduce these values:

We will not savw the project in File > Save Project…

We will next Exit and return to the ISE Project Navigator in order to now Synthetize.

In Processes window Run Synthetize – XST and the process result will be:

Hopefully if everything is right it will be successful as show:

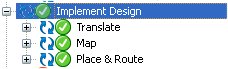

We will now run Implement Design in Processes window and the result will be similar as shown:

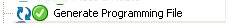

Next we will generate programming bit file, which will be used to program our Spartan 3 board. Run

If all goes well the result on the right side will show success:

The Console window will show:

We will now program our Spartan S3 board. It is assumed that you have the Digilentboard duly configured to “see” the USB Jtag programming cable, and Digilent Adept 2 chaintool is installed in your PC.

Within Processes window choose Configure Run Manage. Right click with your mouse and Run as shown

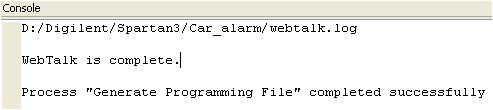

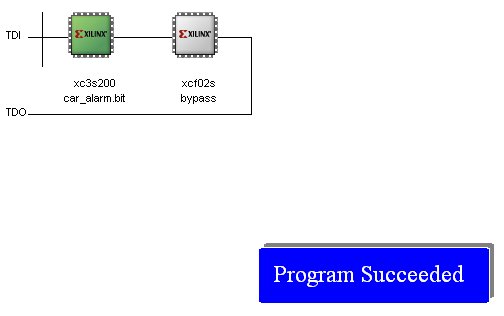

Digilent Adept 2 will open. Click on Boundary Scan:

The empty workspace will show:

Do as it says: Right clich to initialize chain. Choose the option as shown below:

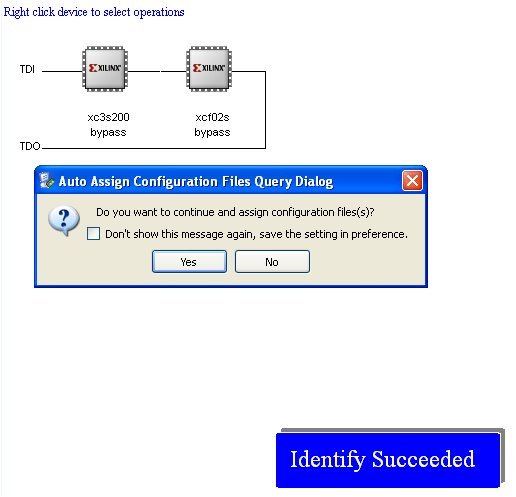

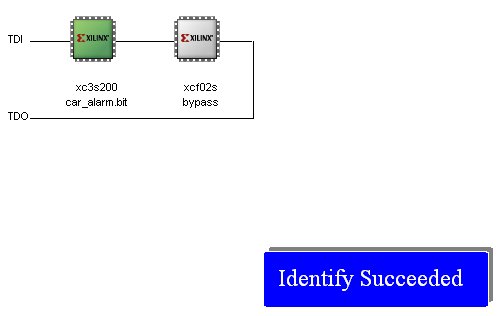

Press Yes button

NOTE: We will not program the PROM. This process requires configuration in Adept 2.0 by launching Create PROM file before doing anything else in ISE Project Navigator.

A window will pop up, and we will introuce the bit file we have generated in our Car_alarm project directory.

A new pop up window will invite us to assign PROM file:

We will press bthe button Bypass. A new window will pop up:

Press OK and the result will be:

We will now right click XC3S200 icon in order to program the board:

Device will be programming and hopefully will be hopefully successful as shown below

Testing the project

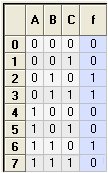

The alarm circuit will light up a LED (LD0) on Spartan 3 Starter kit board only when the key (SW1) is in the ignition and either the door (SW2) is open or the seatbelt (SW0) is not fastened. The variables are:

Hence the Truth table is:

Where A (SW2) = DOOR, B (SW1) = KEY and C (SW0) = BELT.

On Spartan S3 board, from rightmost switch in direction to left, we have BELT, KEY and DOOR.

DEMO Video:

Download

The VHDL, Constraints and bit file can downloaded from here.

Conclusions:

A complete Workflow has been shown in this two parts tutorial of a simple Car Alarm.

From Truth table we have obtained the Boolean expression, and we have simulated in Multisim 12.0 and exported the respective VHDL code.

In this part of tutorial we imported the file in Xilinx ISE Project Navigator, and we did all the procedures to implement the VHDL on an FPGA.

We have sucessfully programmed the Digilent Spartan 3 Starter kit board, and tested our Car Alarm circuit we designed in part I.

Pingback: Designing, Simulating and Implementing a Simple Car Alarm on a Xilinx FPGA – Part I | RedAcacia

Pingback: Finite-State Machine Design of a Simple Car Security Alarm on a Xilinx FPGA – Part I | RedAcacia

Pingback: Design and Simulate a Digital Circuit in NI Multisim and Implement on a Digilent Basys 2 Spartan-3E FPGA Board | RedAcacia