Objectives

Finite-state machine (FSM) or finite-state automaton design of a simple car security alarm using StateCAD, and implementation on a Digilent FPGA Spartan 3 Starter kit board..

In this part we will generate the VHDL code. In part II we will simulate and in part III we will implement the VHDL code in our Digilent Spartan 3 Starter kit board.

Requirements

– StateCAD inside Xilinx ISE Design Suite 10.1

– Digilent Spartan 3 Starter Kit board (for implmentation in part II)

Overview

StateCAD allows visual implementation of a State Diagram and translation into a Hardware Description Language (HDL) code. It is not necessary to understand the HDL code, however we have little control over how the software translates the state diagram.

We will create a state diagram for a car security alarm, and generate VHDL. In part II we will simulate our state diagram to check whether it behaves like we expect. In part III we will create the schematic symbol and implement the VHDL code in our Diglent Spartan 3 board, and finally test the car security alarm to ensure that it works as expected.

Car Security Alarm Specifications

We wil devise a simple Car Security Alarm that will sound a siren if the car alarm system has been energized i.e. armed (A=1) and the door is open (B=1) and / or an ultrasoic sensor signals movement inside the car (C=1).

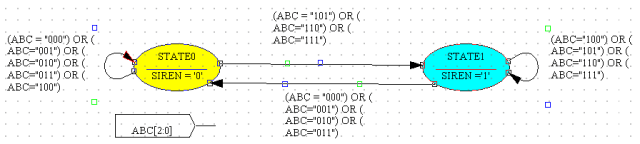

We need to ensure that when the door has been opened in an unauthorized manner, or a presence is detected by the ultrasonic sensor within the car, the alarm siren will sound. This is achieved with a Finite-State Machine (FSM) as shown:

1) In STATE0 the siren is off (SIREN=0) if the alarm is not energized that is armed (A=0) and the door (B) or the ultrasonic sensor (C) can be in any combination, or if alarm is armed (A=1) the siren will not sound if door is closed (B=0) or no presence is detected within the car by the utlrasonic sensor (C=0).

2) There is a transition from STATE0 to STATE1. if alarm is armed (A=1) and if either the door is open (B=1) or ultrasonic sensor detects a presence within the car (C=1) or both the door is open and ultrasonic sesnor detects (B=1 and C=1), the siren will sound, and the system will remain in STATE1.

3) The system will remain in STATE1 that is. siren will be sounding whatever happens next to the door (either is closed or open or sensor detects or not, provided the alarm is still armed (A=1).

4) Transition from STATE1 to STATE0 occurs only if the system is desarmed (A=0). and in this circunstance for B or C, the siren will not sound anymore (SIREN=0).

Creating the Diagram in StateCAD

Our aim is to obtain a State Diagram as shown above.

Open StateCAD by navigating thorugh the Start menu: Start -> Programs -> Xlinix ISE Design Suite 10.1 -> ISE -> Accessories -> StateCAD.

Activate the state diagram tool by clicking the Add State icon found in the tool bar:

A state similar to the one shown below appears:

You will draw next State as shown in our proposal for the State Diagram. We will next connect up the two states with transitions by using the tool Add Transition, activating the following icon in the tool bar:

And now draw by clicking and linking to obtain the following result:

And now draw by clicking and linking to obtain the following result:

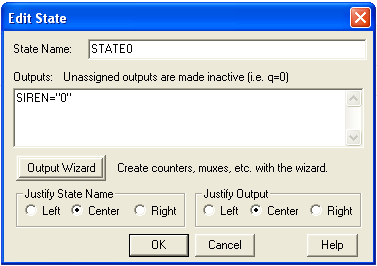

Save the drawing with the name STATE_CAR. Now click onto the STATE0 and Edit State window will pop up:

Do as shown introducing output SIREN=”0″. After finishing click OK, and do the same with STATE1 and add output condtion as SIREN =”1″

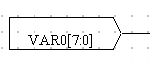

Add variable vector to the drawing by activating Add Vector icon (looking like a yellow bus) in the tool bar:

And place variable vector:

Click onto it and the Edit Vector window will pop up:

Change the name to ABC and the range to 2:0, as shown in the figure and click OK.

We will next change the conditions of the transitions. Click onto the loop back transition of STATE0 and Edit Condition window will pop up:

Introduce Condition: ABC = “000”) OR (ABC=”001″) OR (ABC=”010″) OR (ABC=”011″) OR (ABC=”100″) . And press OK

Edit all other transitions to obtain the following final result:

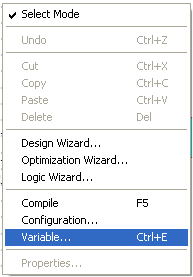

We are now ready to ckeck variables. Right click with the mouse onto an empty area of the drawing and the follwing menu will pop up where you will choose Variable… .:

The window with Variables will pop up:

If you have done everything right the window will show all the variables in your drawing. Click OK.

NOTE: You can make modifications here if it is required.

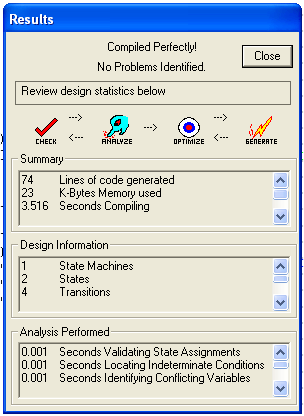

We are now ready to compile. Click Generate VHDL icon on top tool bar just below top menu:

If everything is OK, following window will pop up:

NOTE: Warning windows may pop up before Results, to tell you for example that compilation has found remnants of variables you may have added and invitate you to delete them, that you must do.

A window will pop up if you Close the window, showing the VHDL code that has been generated:

NOTE. You can check now if the code makes sense, but can do nothing else apart going back to the drawn project and edit it.

We are just about ready to simulate the state diagram and implement the VDL code in our Xilinx FPGA, something that we will do in parts II and III of this tutorial.

Download

The drawing and generated VHDL files can be downloaded from here.

Acknowledgements

A special credit is due to Examples from Class pdf found at University of Wrocester site, for the state diagram. This tutorial uses a completely different approach to achieve the code generation.

Conclusions

We have designed a State Diagram in StateCAD and compiled a VHDL file. In part II we will simulate the state diagram and in part III we will program our Digilent Spartan 3 board, and test physically the logic circuit.

Pingback: Finite-State Machine Design of a Simple Car Security Alarm on a Xilinx FPGA – Part II | RedAcacia

Pingback: Finite-State Machine Design of a Simple Car Security Alarm on a Xilinx FPGA – Part III | RedAcacia