Objectives

Implement on actual hardware, a Xilinx Spartan 3 Starter kit board from Digilent, with VHDL code generated after having designed a simple car security alarm using StateCAD in part I.

Requirements

– Xilinx ISE Design Suite 14.2

– Digilent Spartan 3 Starter Kit board.

Car Security Alarm Specifications

We wil devise a simple Car Security Alarm on actual hardware, a Digilent Spartan Starter KIt board, that will sound a siren ( LD0 will switch on in our Spartan 3 board) if the car alarm system has been energized i.e. armed (A=1, that is SW7 in our Spartan 3 board ) and the door is open (B=1, that is SW1 in our Spartan 3 board) and / or an ultrasonic sensor signals movement inside the car (C=1, that is SW0 in our Spartan 3 board).

Implementation on a FPGA

Launch Xilinx ISE Design Suite, get into the Project Navigator, and start a New Projectpressing the button for New Project. Xilinx ISE Project Navigator controls all aspects of the development flow of our FPGA. We will use it to launch all development tasks.

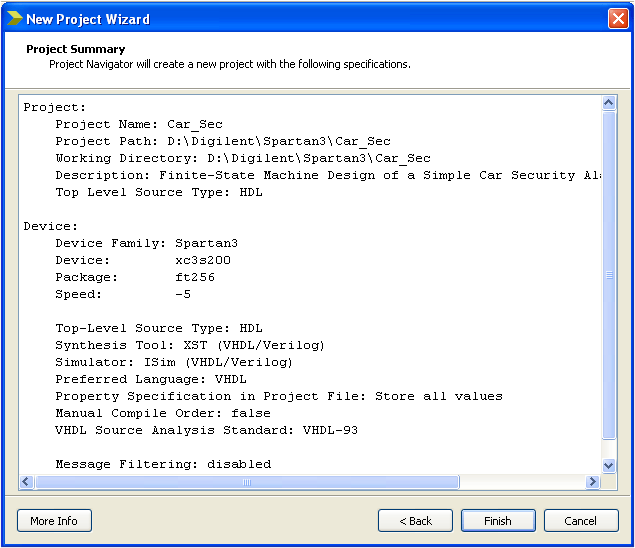

Give the project a name such as Car_Sec and fill all the fields appropriately, including pointing to the drive and directory in your PC where you will keep the project files:

Click on Next button and the following window will open:

Do the required changes as shown on the image and click Next button. The following window will open:

Click Finish button. The Project Navigator will show an empty view of the Hierachy window of our project:

Now we add the VHDL source we have generated in part I:

The following window will open which will hopefully do a sucessful adding of source:

Press Ok button.

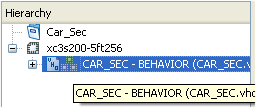

The Project Navigator will show a summary of what has been done so far and the source code will show up in Hierarchy window. Highlight the Car_Sec.vhd file and double click on it:

The full VHDL code will be shown in the right window of our Project Navigator:

We are now ready to check syntax, and do further preparations for implementation.

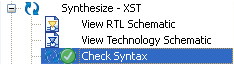

In the Processes window we run Check Syntax

The results hopefully will be Ok as shown:

We will next see our schematic. We will first run Create Schematic Symbol in Processes window:

Now run View RTL Schematic in Processes window:

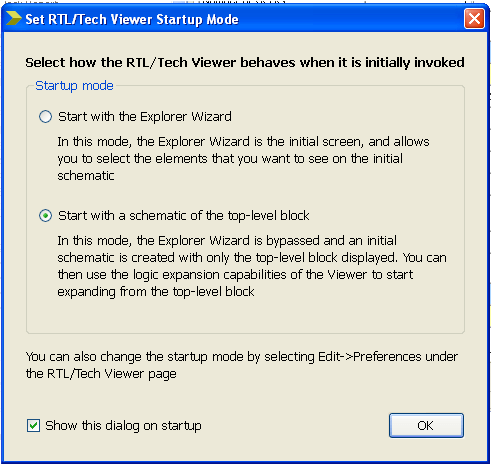

Viewer Startup Mode window will pop up, where we will choose the second choice as shown:

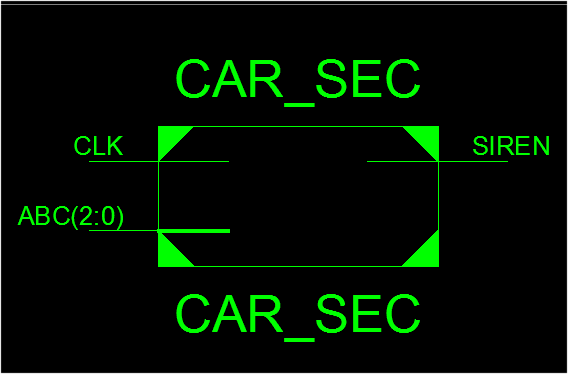

Click Ok. In the right window of Project Navigator we will see the main schematic:

If we click the block diagram, we will see:

By clicking LUT4 block we will see the logic circuit:

We are now ready to create contraints, i.e. configuration of inputs and outputs in our Digilent Spartan 3 Starter kit board. In Processes window run I/O Pin Planning (PlanAhead):

A window will pop up to tell us that no constraints file have been created:

We click Yes button. PlanAhead will open with Welcome to Plan Ahead window popping up:

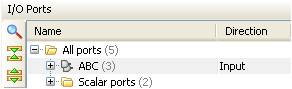

After tcl file has run automatically, we have to close this window and concentrate on I/O Ports window of PlanAhead:

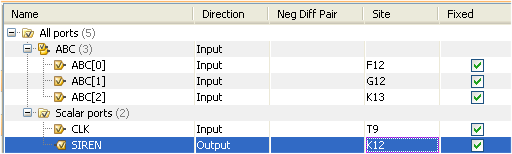

Clicking on ABC and Scalar ports we will expand these folders. And we start to introduce constraints referring to our Digilent Spartan 3 Starter kit board as shown.

We introduce the riht input and output pins. Please refer to Digilent Spartan 3 Starter kit manual.

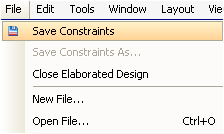

We are now ready to save Constraints in File -> Save Constraints as shown:

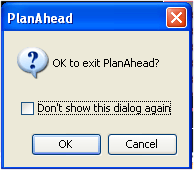

Leave PlanAhead with File -> Exit

Press OK as in following window:

We are now back to Project Navigator where we will see our constraints file we have just created:

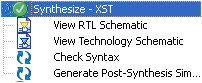

We wii proceed to Processes window and run Synthetize-XST as shown:

Hopefully results will be of sucessful synthesis:

We next will run Implement Design:

And the results will be again hopefully of sucessful process:

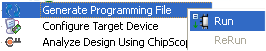

Finally we are ready to generate the bit file with which we will program our Digilent Spartan 3 Starter kit board:

Programming file will be generated hopefully:

And the Console window will show the results of the process:

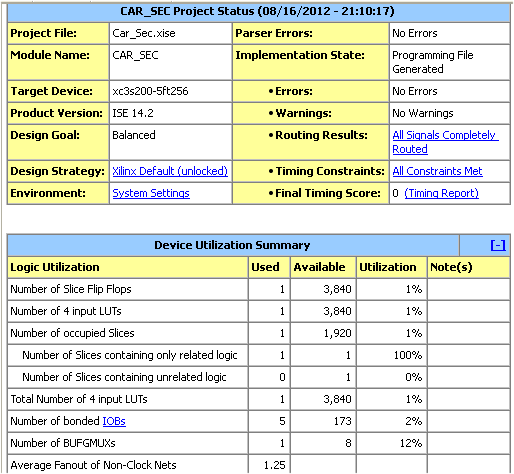

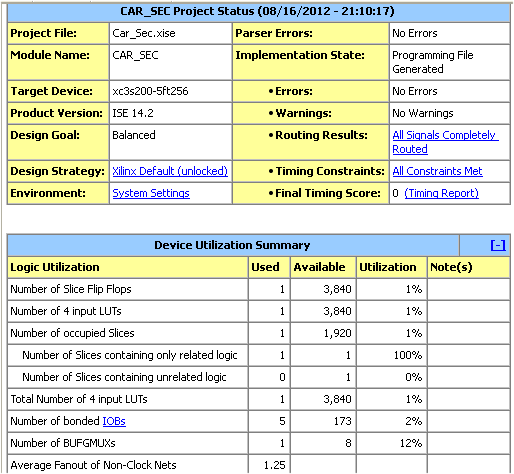

The right window of our Project Navigator will give us the summary of our project:

We are finally ready to implement after checking out the summary that everything is right.

We will now program in our Spartan 3 board. It is assumed that you have the Digilent board duly configured to “see” the USB Jtag programming cable, and Digilent Adept 2 chaintool is installed in your PC.

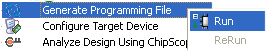

Within Processes window choose Generate Programminf file. Right click with your mouse and Run as shown

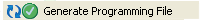

Programming file will be generated hopefully with success:

Finally we will program our Digilent Spartan 3 Starter kit board:

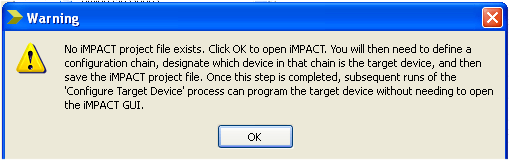

A pop up window will open:

Click OK. Xilinx ISE Impact will open with empty workspace:

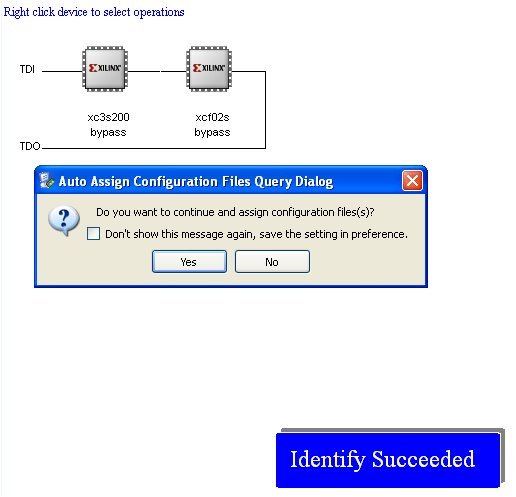

Double click on Boundary Scan. The empty workspace will now show:

Do as it says: Right click to initialize toolchain. Choose the option as shown below:

The result will be:

A sucessful identification has occured. Press Yes button.

NOTE: We will not program the PROM. This process requires configuration in Adept 2.0 by launching Create PROM file before doing anything else in ISE Project Navigator.

A window will pop up, and we will introduce the bit file we have generated in our Car_Sec project directory.

Assign the bit file and click Open

A new pop up window will invite us to assign PROM file:

Click Bypass. A new window will pop up:

Press OK and the result will be:

We will now right click XC3S200 icon in order to program the board and choose Program:

Device will be programmed and hopefully will be hopefully successful as shown below

A succesful programming has been done.

Testing the project

The alarm security circuit will light up a LED (LD0) on Spartan 3 Starter kit board, simulating SIREN sounding, only when the conditions we have established of state machine occurs. Test the state machine as shown:

On Digilent Spartan 3 board, the leftmost switch represents ALARM armed or unarmed (upward or downward respectively) the rightmost switches are DOOR (upward door open, downward door closed) and ULTRASONIC SENSOR (upward presence detected and downward no presence).

DEMO Video:

Download

The board Constraints and bit file can be downloaded from here.

Conclusions:

A complete Workflow has been shown in this three parts tutorial of a simple Car Security Alarm using Finite-State Machine to design the logic circuit.

We first designed the State Diagram in StateCAD and generated VHDL, then we simulated our state diagram in StateCAD to verify whether it behaves as expected.

In this part of our tutorial, we imported the VHDL file of part I in Xilinx ISE Project Navigator, and we followed all the procedures to implement our VHDL in an FPGA.

We have sucessfully programmed the Digilent Spartan 3 Starter kit board, and tested our Car Security Alarm state machine we designed in part I.

Pingback: Finite-State Machine Design of a Simple Car Security Alarm on a Xilinx FPGA – Part I | RedAcacia

Pingback: Finite-State Machine Design of a Simple Car Security Alarm on a Xilinx FPGA – Part II | RedAcacia

good job!!

but what is cost of Digilent Spartan 3 Starter Kit board??

Welcome to my blog. The kit costs $169 and you will need a Jtag programming cable.

we want program in verilog

Welcome to my blog. So what is your difficulty in generating Verilog code?

hello , I NEED Security/Intruder Alarm vhdl code.

Just check the project done here and make adequate changes.

please provide the complete code for car security system

Sorry to reply that late. No I do not have any complete code.